## 光纤通信 ctc 模式测试例程

## 1 实验简介

Pango 的 Logos2 系列 FPGA 集成了串行高速收发器 HSSTLP，可以实现高速串行数据通信。在 AXP100 开发板上，FPGA 的 HSSTLP 的 2 个收发器通道已经连接到 2 路 SFP 光模块接口，用户只需要另外购买 SPF 的光模块就可以实现光纤的数据传输。本实验将介绍通过光纤进行板间连接实现光模块之间的数据收发测试。

## 2 实验原理

### 2.1 HSSTLP 介绍

HSSTLP 原理介绍参考《光纤通信测试例程》教程中的内容，这里不再重复。

### 2.2 硬件介绍

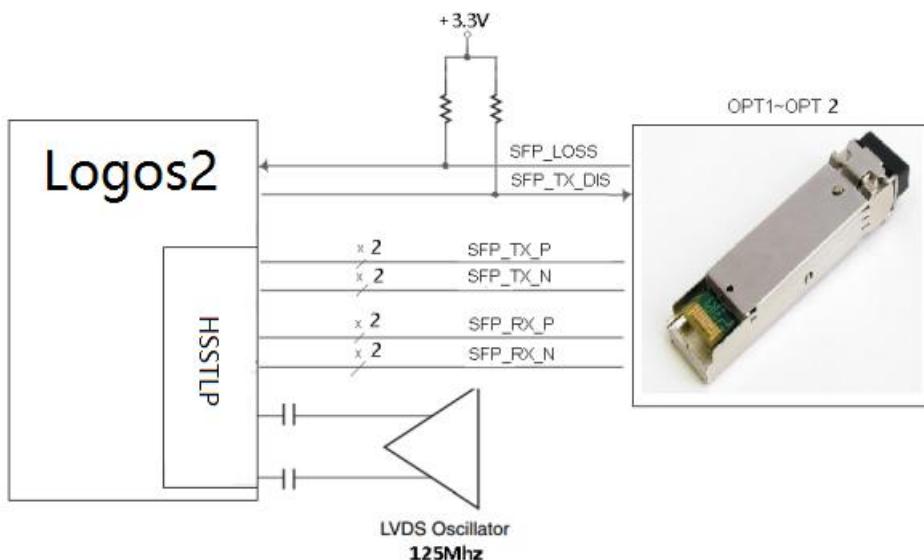

在开发板上，有 2 路光纤接口 SFP1~SFP2，分别连接到 FPGA 芯片的 HSSTLP 的通道上。FPGA 和光纤连接的设计示意图如下图所示：

其中 SFP1 光模块接口连接到 Q3 HSSTLP 的 Channel3 上，SFP2 跟 Q3 HSSTLP 的的 Channel2 相连。光模块和 FPGA 之间用 0.1uf 的电容隔开，使用 AC Couple 的模式。

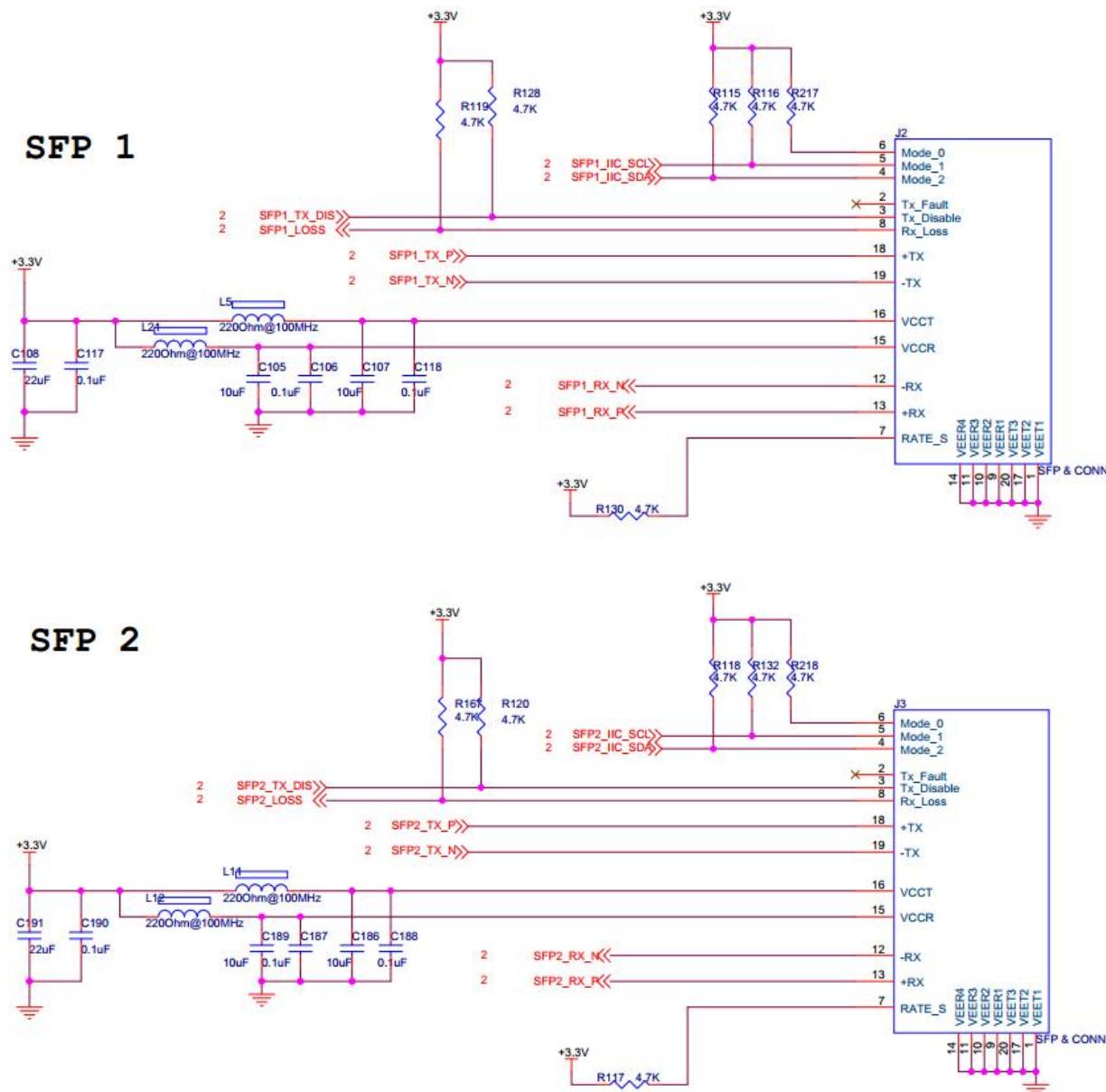

光模块的 LOSS 信号和 TX\_Disable 信号连接到 FPGA 的普通 IO 上。LOSS 信号用来检测光模块的光接收是否丢失，如果没有插入光纤或者 Link 上，LOSS 信号为高，否则为低。TX\_Disable 信号用来使能或者不使能光模块的光发射，如果 TX\_Disable 信号为高，光发射关闭，否则光发送使能，正常使用的时候需要拉低此信号。硬件原理图如下：

### 3 程序设计

我们先来测试一下开发板上的 HSSTLP 模块工作是否正常。以下是具体测试步骤：

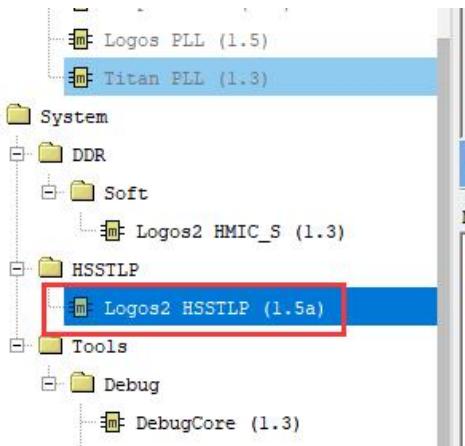

1. 新建一个工程 hsst\_core，在 tools 菜单栏下 IP Compiler 添加 HSST IP， ipm2l\_hsstlp\_v1\_5a.iar IP 在 hsst\_test 文件夹下，添加 IP 在《DDR3 读写测试实验》教程中已讲过，这里不再重复。

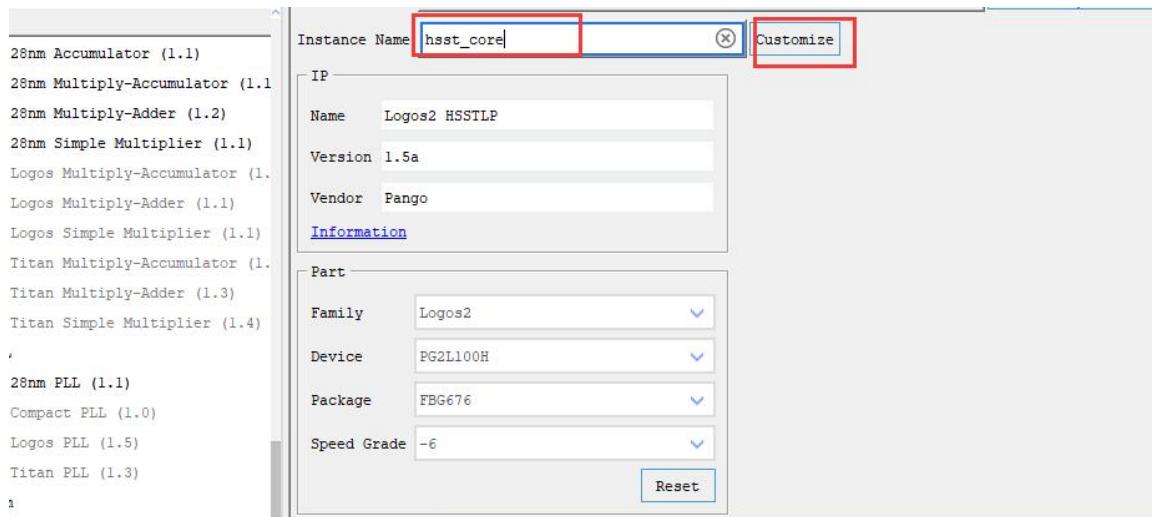

2. 新建 HSSTLP IP 并命名为 hsst\_core，再单击 Customize；

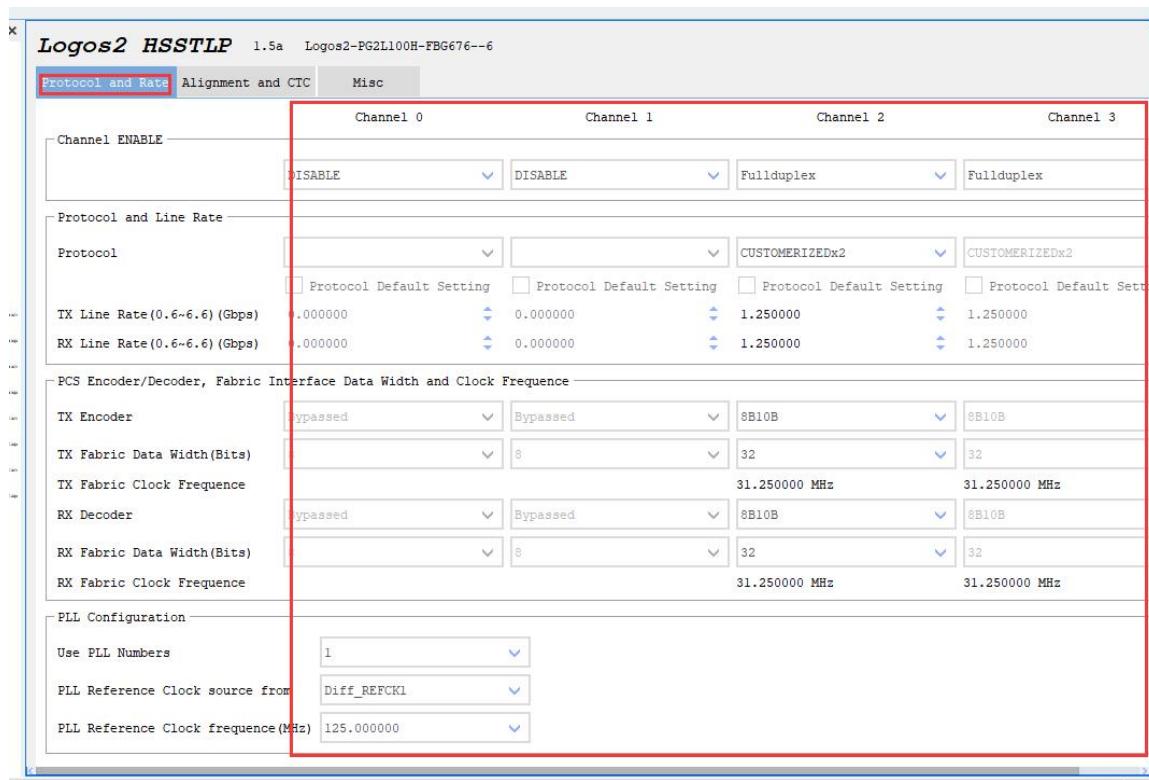

3. 在弹出的界面中 Protocol and Rate 栏中按如下设置， Channel0 Channel1 为 DISABLE， Channel2 Channel3 为 FullDuplex 由硬件决定，速率：1.25G，数据位宽：32 位，选择 8/10 编解码，参考时钟为 Diff\_REFCK1，频率 125M，Protocol 为 CUSTOMERIZEDX2; 如下图所示：

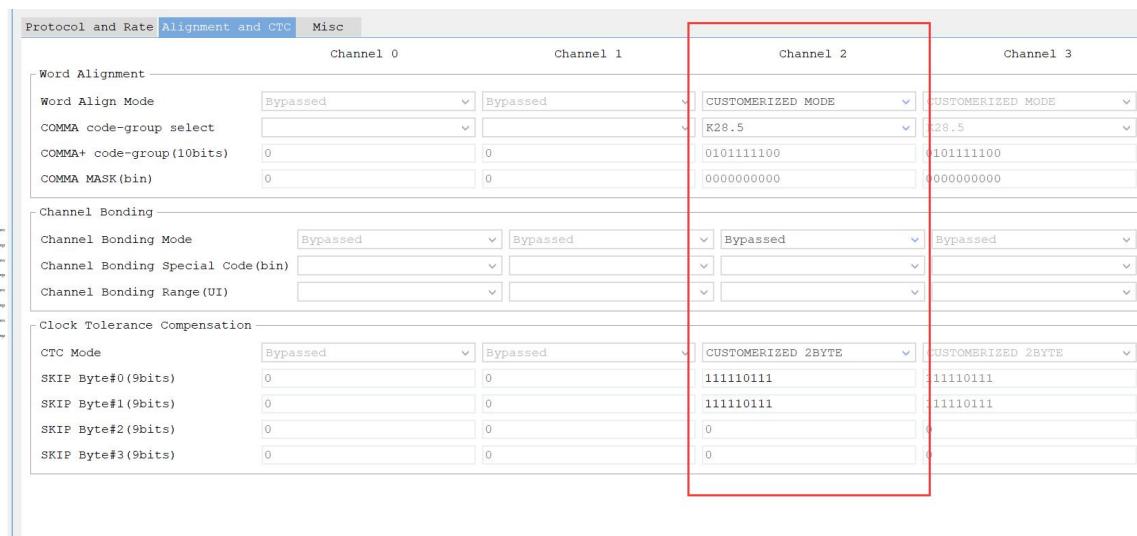

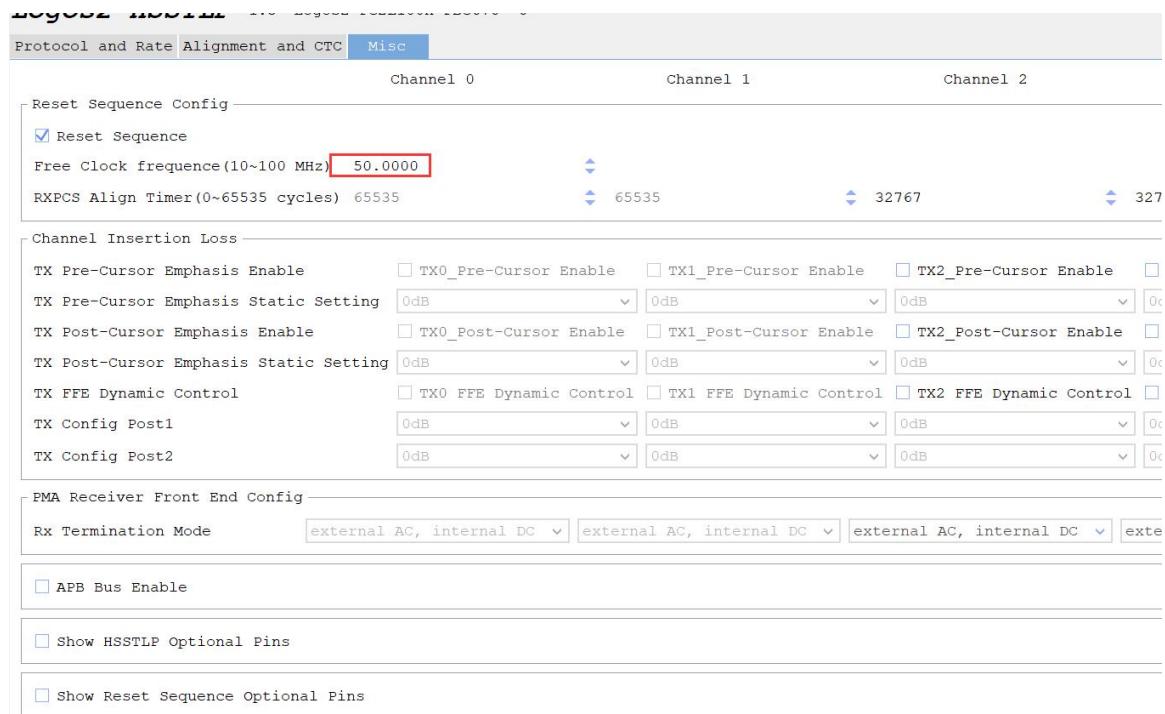

4. 在 Alignment and CTC 栏中采用 CUSTOMIZED\_MODE 和 CTC 模式； Misc 栏中时钟为 50MHZ，

其它默认：

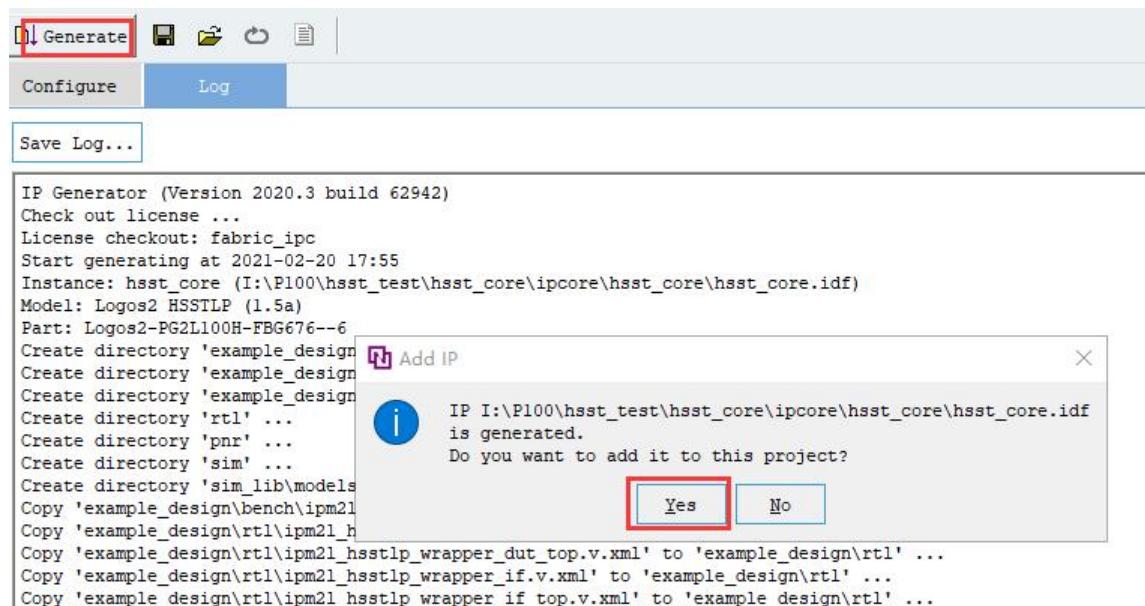

5. 单击 Generate 产生 IP 即可，并单击“Yes”，软件会自动生成 demo。

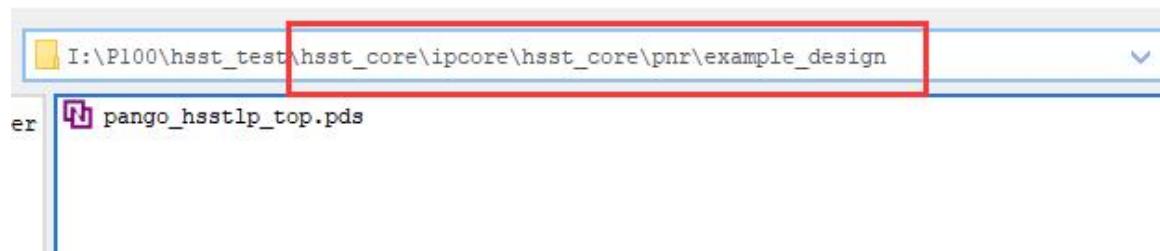

6. 打开软件生成的 demo 工程在如下位置：

The screenshot shows the ALINX IP Generator software interface. The left sidebar displays the project structure under 'PG2L100H-6FBG676'. Under 'Designs', there is a selected item 'hsst\_core\_dut\_top (hsst\_core\_dut\_top.v)'. Other items include 'U\_INST - hsst\_core (hsst\_core.v)', 'U\_INST\_SRC - hsst\_core\_src (hsst\_core\_src.v)', and several 'chk\_rstn\_sync' components. Under 'Constraints', there is a file 'pango\_hsstlp\_top.fdc'. Under 'Simulation', there is a file 'hsst\_core\_dut\_top.sva'. The right panel shows the code editor for 'hsst\_core\_dut\_top.v'. The code is a Verilog module definition for 'hsst\_core\_dut\_top' with various input and output ports. The top of the code includes copyright and license information.

```

1 // Created by IP Generator (Version 2020.3 build 62942)

2

3

4 //////////////////////////////////////////////////////////////////

5 //

6 // Copyright (c) 2019 PANGO MICROSYSTEMS, INC

7 // ALL RIGHTS RESERVED.

8 //

9 // THE SOURCE CODE CONTAINED HEREIN IS PROPRIETARY TO PANGO MICROSYSTEMS, IN

10 // IT SHALL NOT BE REPRODUCED OR DISCLOSED IN WHOLE OR IN PART OR USED BY

11 // PARTIES WITHOUT WRITTEN AUTHORIZATION FROM THE OWNER.

12 //

13 //////////////////////////////////////////////////////////////////

14 //

15 // Library:

16 // Filename:

17 //////////////////////////////////////////////////////////////////

18 `timescale lns/100fs

19

20 module hsst_core_dut_top (

21     input    i_free_clk,

22     input    i_pll_rst_0,

23     input    i_wtchdg_cir_0,

24     output   [1:0] o_wtchdg_st_0,

25     output   o_pll_done_0,

26     output   o_txlane_done_2,

27     output   o_txlane_done_3,

28     output   o_rxlane_done_2,

29     output   o_rxlane_done_3,

30     input    i_p_refckn_1,

31     input    i_p_refckp_1,

32     output   o_p_pll_lock_0,

33     output   o_p_rx_sigdet_sta_2,

34     output   o_p_rx_sigdet_sta_3

35 );

```

7. 为了适合开发板硬件电路设计，主要对 hsst\_core\_dut\_top.v 的复位进行修改，进行统一复位，增加调试接口测试，修改管脚分配，其它不变，然后程序编译综合产生位流文件。

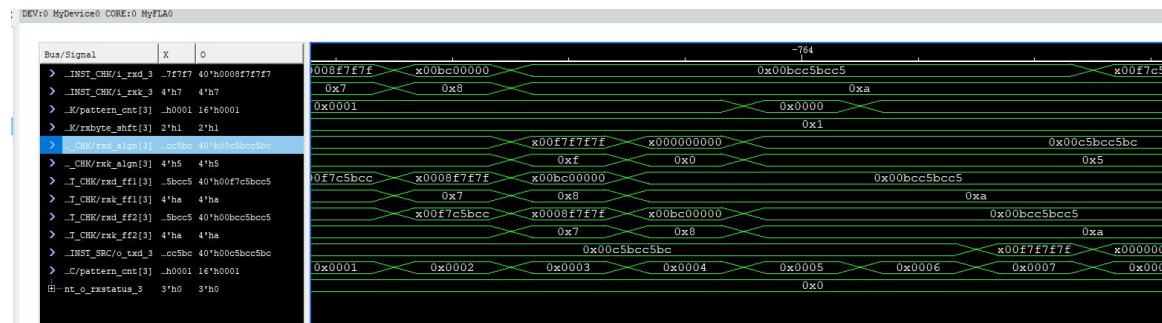

8. 把光纤两端接入接口 SFP1 和 SFP2 进行环路测试，下载程序到开发板中进行在线调试，可看到窗口中发送和接收的数据一致的。

## 4 实验现象

开发板自身是不带 SFP 的光模块和光纤的，所以测试之前需要自己准备 SFP 的光模块和光纤。因为光纤传输至少需要 2 个光模块，用户需要准备 2 个 SFP 光模块才是做光纤通信实验。10G 或者 1.25G SFP 的光模块和光纤再淘宝上都能购买到，在购买 SFP 光模块的同时，同时让商家提供配套的光纤就可以了。

测试之前我们把 SFP 的光模块分别两个 AXP100 开发板上，再用光纤把光模块 SFP1 与另一个开发板的 SFP1 对连起来。因为这里我们用的光模块及光纤是 TX 和 RX 是分开的，这样 SFP1 光模块 RX 需要跟 SFP2 光模块的 TX 相连，SFP1 光模块的 TX 需要连接到 SFP2 光模块的 RX。

下载程序到开发板中进行在线调试，可看到窗口中发送和接收的数据一致的。